Versatile Express 主板/母板μATX用户手册

| 软件大小:926 KB | 软件性质: 免费软件 |

| 更新时间:2013/9/4 18:17:57 | 应用平台:Win9X/Win2000/WinXP |

| 下载次数:8410 | 下载来源:完美体育·(中国)手机网页版科技 |

| 软件语言:英文 | 软件类别:ARM官方开发平台 > |

|

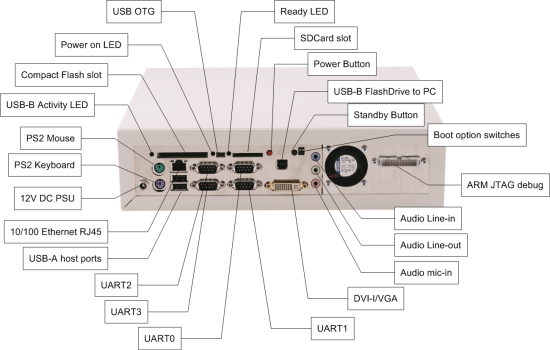

此主板有两组子板牛角连接器。它必须始终与处理器子板 Express 或软宏模型子板配对使用以提供主系统处理器。可以添加可选的逻辑子板 Express 板以提供自定义 IP 开发和验证功能。

- 配备各种有用的外设接口

- 适用于 Versatile Express 子板的拖放式 USB 驱动器配置机制

- 功能强大的启动监视器程序可以配置子板并启动应用软件映像

- 单元预先装载了 Debian Linux 安装程序

- 可以通过 RS232 端口远程控制系统电源并重置信号

- 紧凑独立的系统,携带方便并适合进行展示或客户部署

Versatile Express 主板规格参数手册内容目录

Contents

Motherboard Express μATX Technical Reference Manual

Preface

About this book .......................................................................................................... vii

Feedback .................................................................................................................... xi

Chapter 1 Introduction

1.1 About the Motherboard Express μATX .................................................................... 1-2

1.2 Precautions .............................................................................................................. 1-5

Chapter 2 Hardware Description

2.1 Motherboard architecture and buses ....................................................................... 2-2

2.2 Power up, on/off and reset signals .......................................................................... 2-6

2.3 Clock architecture .................................................................................................... 2-9

2.4 Power ..................................................................................................................... 2-11

2.5 Peripherals and interfaces on the motherboard ..................................................... 2-12

2.6 Interrupt signals ..................................................................................................... 2-18

2.7 DMA signals ........................................................................................................... 2-20

2.8 JTAG and test connectors ..................................................................................... 2-21

Chapter 3 Configuration

3.1 Configuration environment ....................................................................................... 3-2

Chapter 4 Programmers Model

4.1 About this programmers model ................................................................................ 4-2

4.2 Memory maps .......................................................................................................... 4-3

4.3 Register summary .................................................................................................... 4-8

4.4 Register descriptions ............................................................................................. 4-10

4.5 IO Peripherals and interfaces ................................................................................ 4-26

Appendix A Signal Descriptions

A.1 Audio CODEC interface ........................................................................................... A-2

A.2 UART interface ........................................................................................................ A-3

Appendix B Specifications

B.1 Timing specifications ............................................................................................... B-2

B.2 Electrical Specification ............................................................................................. B-7

Appendix C Revisions

产品中心

产品中心 服务与支持

服务与支持 关于完美体育·(中国)手机网页版

关于完美体育·(中国)手机网页版 联系我们

联系我们 关注我们

关注我们