基于Zynq-7000高速数据采集解决方案—完美体育·(中国)手机网页版MYD-C7Z010/20-V2开发板

| 文章来源: 发布日期:2022.9.30 浏览次数:2129 次 |

-

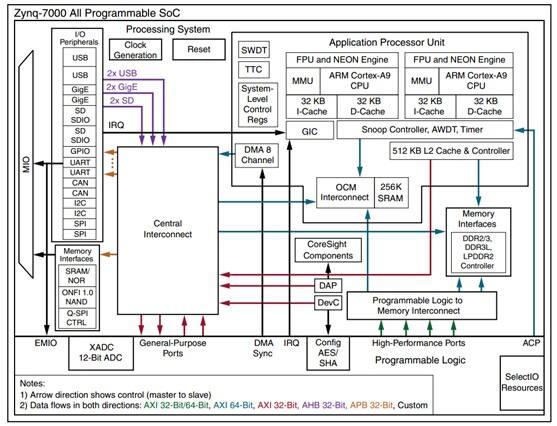

基于 Xilinx Zynq-7000 SoC 高性能低功耗处理器,集成 PS 端单核/双核 Cortex-A9 ARM+ PL 端 Artix-7 架构可编程逻辑资源; -

PS 端最高主频可达 866MHz; -

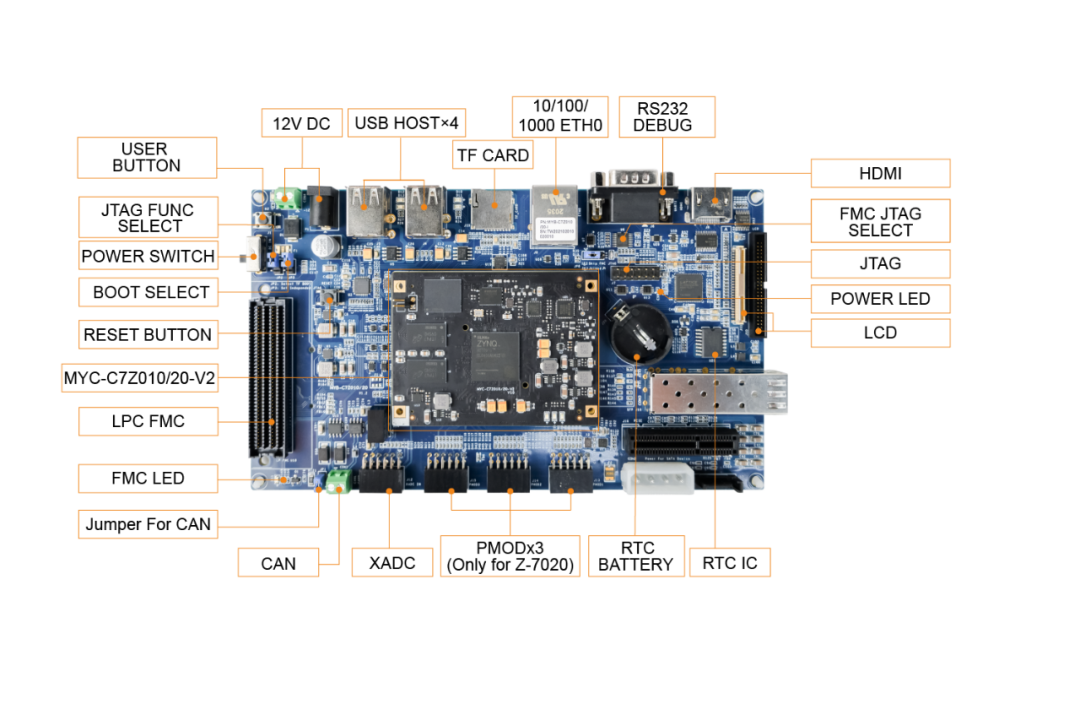

支持 USB 2.0、SDIO、千兆网等多种高速接口,同时支持 I2C、SPI 等常见接口; -

支持两路 12bit MSPS ADC,多达 17 个差分输入通道; -

多达 54 个复用 I/O 引脚,用于外设引脚分配; -

PS 端可通过 EMIO 配置 PL 端 IO,支持共享内存,支持 PS 端和 PL 端数据协同处理; -

PL 端可编程逻辑单元数量区间为 23K-85K,内部集成的 Block RAM 可达 4.9MByte; -

可通过 PS 端配置及烧写 PL 端程序,且 PS 端和 PL 端可以独立开发,互不干扰; -

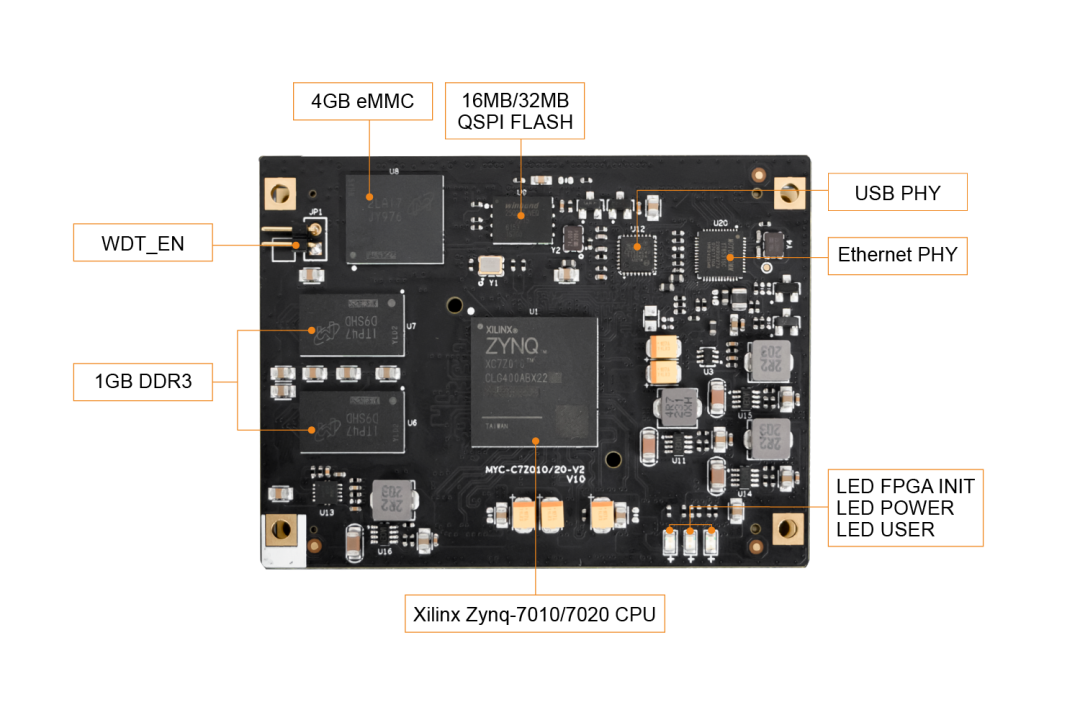

核心板体积极小,大小仅 75mm*55mm; -

连接稳定可靠,采用工业级精密 B2B 常规连接器,保证信号完整性; -

提供 PL 端与 PS 端的片内通信开发教程。

-

提供核心板引脚定义、可编辑底板原理图、可编辑底板 PCB、芯片 Datasheet,缩短硬件设计周期; -

提供系统烧写镜像、内核驱动源码、文件系统源码,以及丰富的 Demo 程序; -

提供完整的平台开发包、入门教程,节省软件整理时间,上手容易; -

提供详细的异构通信开发教程,很好的解决开发瓶颈; -

提供基于 Qt 的图形界面开发教程。

产品中心

产品中心 服务与支持

服务与支持 关于完美体育·(中国)手机网页版

关于完美体育·(中国)手机网页版 联系我们

联系我们 关注我们

关注我们