ARM处理器体系架构详细说明

| 文章来源:完美体育·(中国)手机网页版科技 发布日期:2012.11.13 浏览次数:21790 次 |

ARM 体系结构支持跨跃多个性能点的实现,并已在许多细分市场中成为主导的体系结构。ARM 体系结构支持非常广泛的性能点,因而可以利用最新的微体系结构技术获得极小的 ARM 处理器实现和极有效的高级设计实现。实现规模、性能和低功耗是 ARM 体系结构的关键特性。

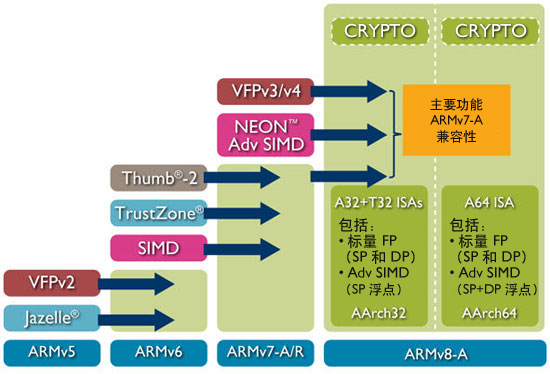

已经开发了体系结构扩展,从而为 Java 加速 (Jazelle)、安全性 (TrustZone)、SIMD 和高级 SIMD (NEON) 技术提供支持。ARMv8-A 体系结构增加了密码扩展作为可选功能。

ARM 体系结构通常描述为精简指令集计算机 (RISC) 体系结构,因为它包含以下典型 RISC 体系结构特征:

- 统一寄存器文件加载/存储体系结构,其中的数据处理操作只针对寄存器内容,并不直接针对内存内容。

- 简单寻址模式,所有加载/存储地址只通过寄存器内容和指令字段确定。

对基本 RISC 体系结构的增强使 ARM 处理器可以实现较高性能、较小代码大小、较低功耗和较小硅面积的良好平衡。

ARMv8 体系结构

ARMv8-A 将 64 位体系结构支持引入 ARM 体系结构中,其中包括:

- 64 位通用寄存器、SP(堆栈指针)和 PC(程序计数器)

- 64 位数据处理和扩展的虚拟寻址

-

两种主要执行状态:

- AArch64 - 64 位执行状态,包括该状态的异常模型、内存模型、程序员模型和指令集支持

- AArch32 - 32 位执行状态,包括该状态的异常模型、内存模型、程序员模型和指令集支持

这些执行状态支持三个主要指令集:

- A32(或 ARM):32 位固定长度指令集,通过不同体系结构变体增强部分 32 位体系结构执行环境现在称为 AArch32

- T32 (Thumb),以 16 位固定长度指令集的形式引入,随后在引入 Thumb-2 技术时增强为 16 位和 32 位混合长度指令集。部分 32 位体系结构执行环境现在称为 AArch32

- A64:提供与 ARM 和 Thumb 指令集类似功能的 32 位固定长度指令集。随 ARMv8-A 一起引入,它是一种 AArch64 指令集。

ARM ISA 不断改进,以满足前沿应用程序开发人员日益增长的要求,同时保留了必要的向后兼容性,以保护软件开发投资。在 ARMv8-A 中,对 A32 和 T32 进行了一些增补,以保持与 A64 指令集一致。

A32(ARM)

ARM(通常称为 A32)是一种固定长度(32 位)的指令集。它是 ARMv4T、ARMv5TEJ 和 ARMv6 体系结构中使用的基础 32 位 ISA。在这些体系结构中,该指令集用于需要高性能的应用领域,或用于处理硬件异常,如中断和处理器启动。

对于性能关键应用和旧代码,Cortex 体系结构的 Cortex-A 和 Cortex-R 配置文件也支持 ARM ISA。其多数功能都包括在与 Thumb-2 技术一起引入的 Thumb 指令集中。Thumb (T32) 从改进的代码密度中获益。

ARM 指令的长度为 32 位,需要 4 字节边界对齐。

可以对大多数 ARM 指令进行“条件化”,使其仅在以前的指令设置了特定条件代码时执行。这意味着,如果应用程序状态寄存器中的 N、Z、C 和 V 标志满足指令中指定的条件,则指令仅对程序员的模型操作、内存和协处理器发挥其正常作用。如果这些标记不满足此条件,则指令会用作 NOP,即执行过程正常进入下一指令(包括将对异常进行任意相关检查),但不发挥任何其他作用。此条件化指令允许对 if 和 while 语句的一小部分进行编码,而无需使用跳转指令。

条件代码包括:

| 条件代码 | 含义 |

|

N |

否定条件代码,如果结果为否定的,则设置为 1 |

|

Z |

零条件代码,如果指令的结果为 0,则设置为 1 |

|

C |

进位条件代码,如果指令生成进位条件,则设置为 1 |

|

V |

溢出条件代码,如果指令生成溢出条件,则设置为 1。 |

T32(Thumb)

成本敏感型嵌入式控制应用领域(例如手机、磁盘驱动器、调制解调器和寻呼机)一直在寻求通过某些方式在兼顾内存占用空间的前提下以最低成本实现 32 位性能和地址空间。

Thumb (T32) 指令集提供已压缩至 16 位宽操作码的、最常用的 32 位 ARM 指令的子集。在执行时,这些 16 位指令实时、透明地解压缩为完整 32 位 ARM 指令,且无性能损失。

Thumb 可向设计人员提供:

-

卓越的代码密度,可实现最小的系统内存大小和最低的成本。

- 在 8 位或 16 位总线上的 8 位或 16 位内存中实现 32 位性能,从而降低系统成本。

- 建立的 ARM 功能

- 行业领先的 MIPS/Watt,以尽可能延长电池寿命和增加 RISC 性能

- 小的芯片面积,以进行集成和尽可能降低芯片成本

- 全球多合作伙伴源,可提供安全保证。

设计人员可以同时使用 16 位 Thumb 和 32 位 ARM 指令集,这样,他们就可以灵活地根据应用需求在子例程级别上增强性能或调整代码大小。

Thumb ISA 受 ARM 生态系统的广泛支持,包括完善的 Windows 软件开发环境以及开发和评估卡。

改进了代码密度,具有性能效率和功效

Thumb-2 技术使 Thumb 成为固定(32 位和 16 位)长度指令集,是所有 ARMv7 兼容的 ARM Cortex 实现所通用的指令集。Thumb-2 提升了众多嵌入式应用程序的性能、能效和代码密度。

该技术与现有 ARM 和 Thumb 解决方案向后兼容,同时显著扩展了 Thumb 指令集的可用功能,从而使更多应用程序从 Thumb 的同类最佳代码密度中获益。为获得性能优化的代码,Thumb-2 技术使用少于 31% 的内存以降低系统成本,同时,提供比现有高密度代码高出 38% 的性能,因此可用于延长电池寿命,或丰富产品功能集。

本文来自完美体育·(中国)手机网页版科技,原文地址:

/customerService/resource-list.asp?id=436,转载请注明出处。

产品中心

产品中心 服务与支持

服务与支持 关于完美体育·(中国)手机网页版

关于完美体育·(中国)手机网页版 联系我们

联系我们 关注我们

关注我们