Xilinx XCZU3EG开发笔记(基于MYD-CZU3EG开发板)

| 文章来源:完美体育·(中国)手机网页版科技 发布日期:2019.8.22 浏览次数:8867 次 |

开发环境:vivado 2017.4,开发板型号:完美体育·(中国)手机网页版MYD-CZU3EG, 主芯片XCZU3EG-1SFVC784。这个系列板子还有4EV,5EV等版本,手里的3EG版本不支持SFP,因此板上相应接口(白色部分)是空贴的。MYD-CZU3EG开发板是基于基于Xilinx XCZU3EG全可编程嵌入式处理器,4核Cortex-A53(Up to 1.5GHZ)+FPGA(154KLE)性能强大。板载4GB DDR4 SDRAM(64bit ,2400MHZ) 及丰富的存储资源,从容应对复杂运算,千兆以太网PHY 和USB PHY , 轻松实现高速互联。

Vivado 自带了许多的 IP 核,像 CAN, UART, SPI 等,如果 CPU 自带的这些资源不够用,可以在 PL 端扩展,关于这些 IP 核的资料,可以在 DocNav 中查找, DocNav 在安装Vivado 软件的时候会自动安装, DocNav 还包含很多其他的资料,如 Vivado, SDK 的使用,还有视频教程。本章会介绍怎样使用 xilinx的 gpio 核,在 PL 端实现一个 gpio 控制器,控制LED。

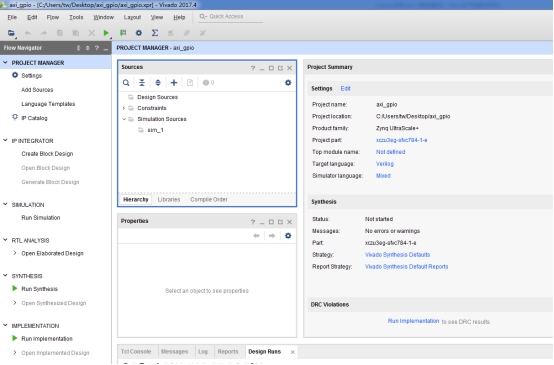

生成的vivado工程(如果不知道如何生成可以参考前面的工程)

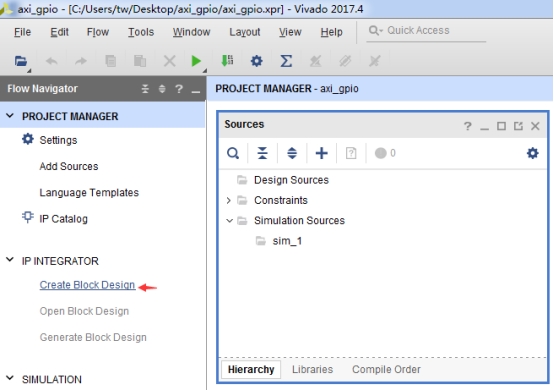

Step1新建Block Design

点击Create Block Design

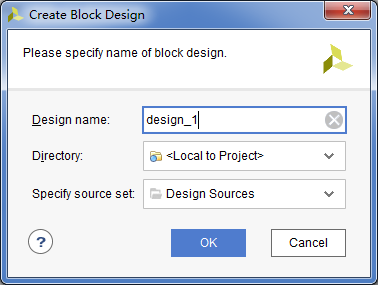

点击OK

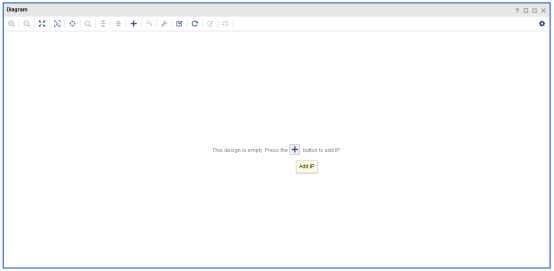

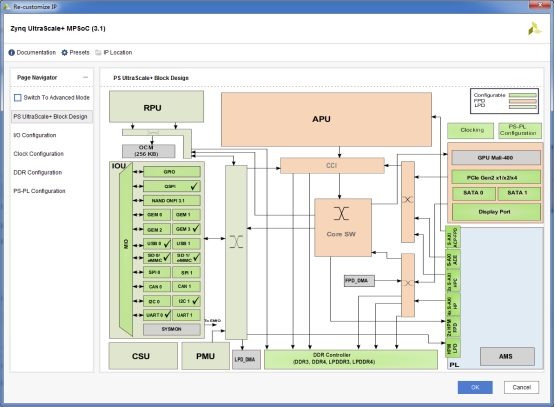

Step2添加PS的IP核并配置

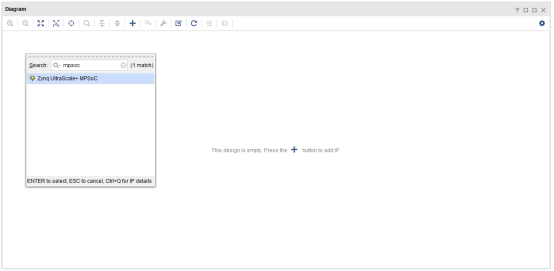

点击Add IP添加IP核

输入mpsoc,然后双击Zynq UltraScale+MPSoC添加mpsoc核

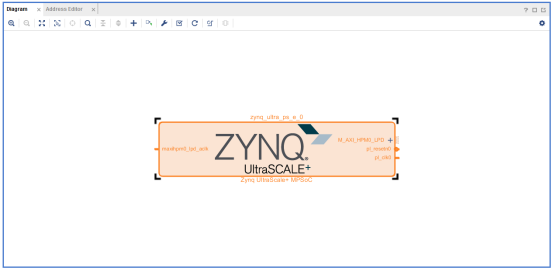

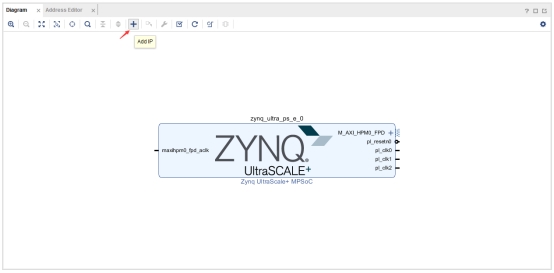

zynq mpsoc核如下图所示

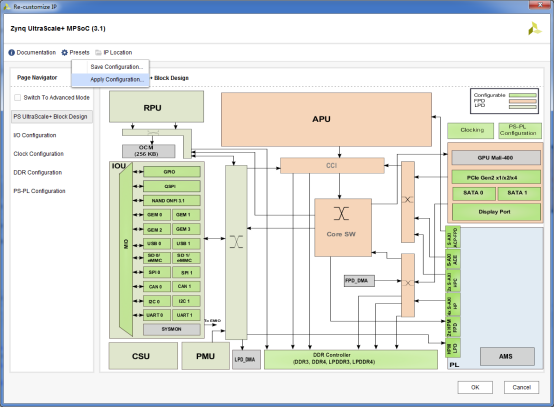

双击zynq mpsoc核导入配置文件

Presets-->Apply Configuration

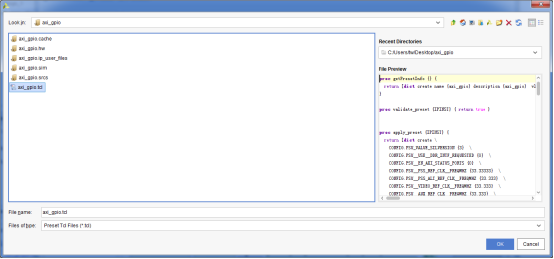

导入axi_gpio.tcl 配置文件,然后点击OK

点击OK

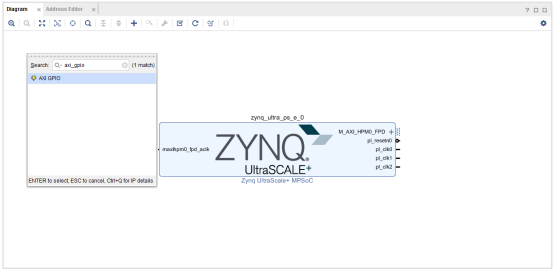

Step3添加axi_gpio IP核并配置

点击Add IP添加IP核

输入axi_gpio,然后双击AXI GPIO添加axi_gpio核

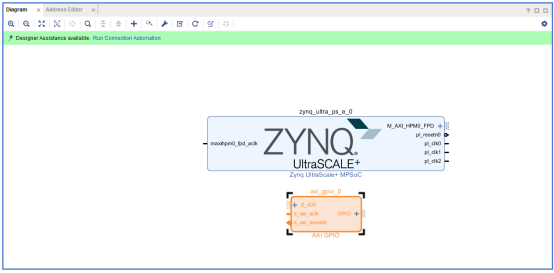

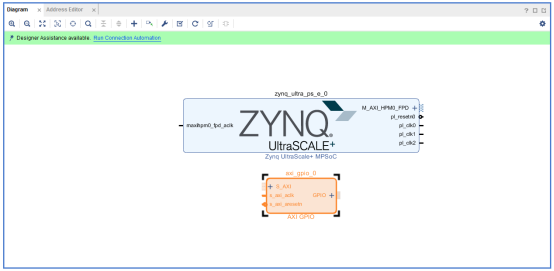

添加的axi_gpio核,如下图所示

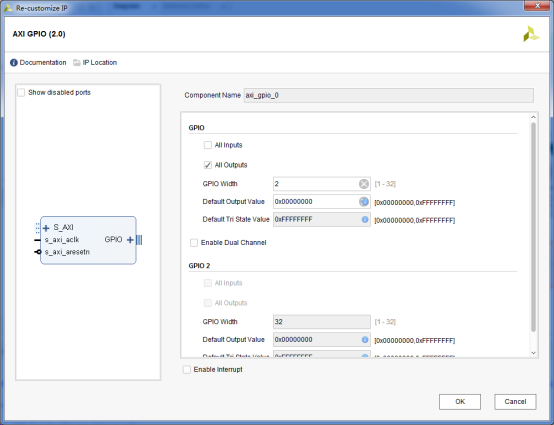

双击axi_gpio核设置参数,勾选All Outputs 、GPIO Width设置为2,点击OK

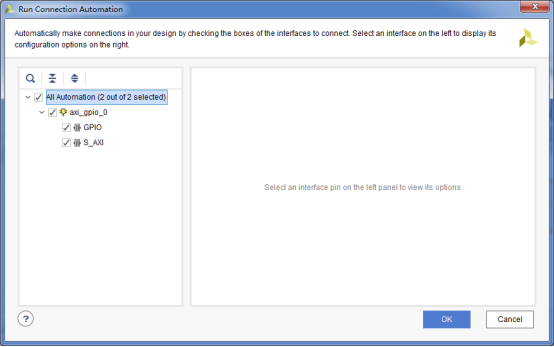

点击Run Block Automation->OK进行自动连线

勾选所有选项,点击OK

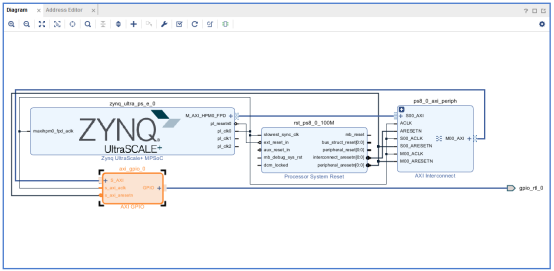

自动连线完成后,如下图所示

Step4 生成综合文件

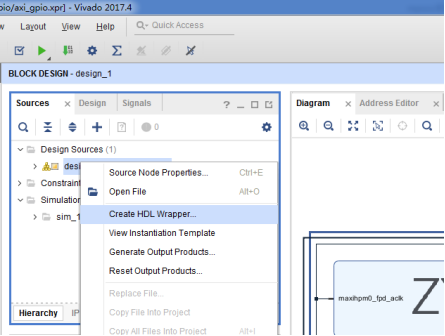

右击 design_1->Generate Ouput Products->Generate

Step5 生成FPGA顶层文件

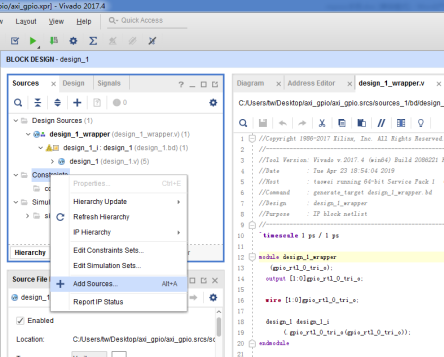

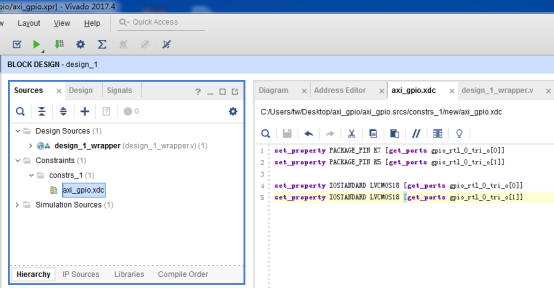

Step6 添加xdc管脚约束

右击Constraints-->Add Sources

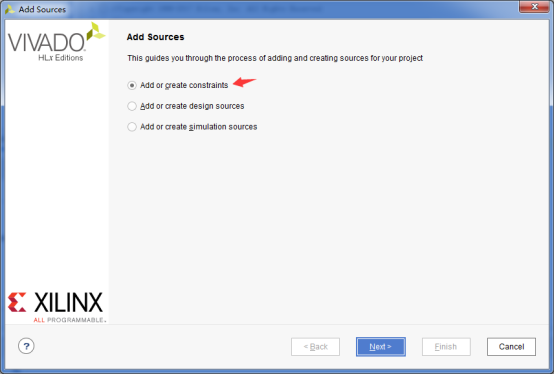

选择Add create constraints,点击Next

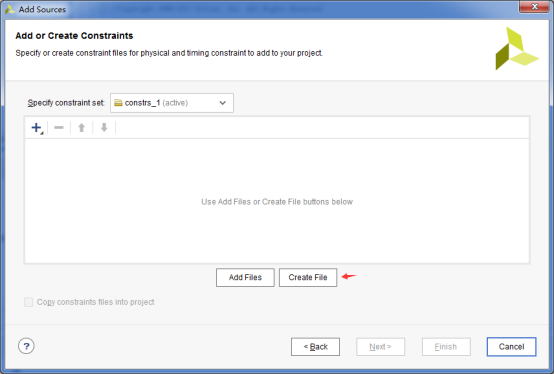

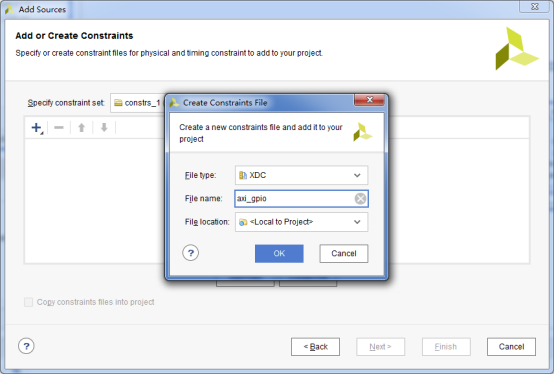

点击Create File

输入新建的xdc文件名称,点击OK

点击Finish

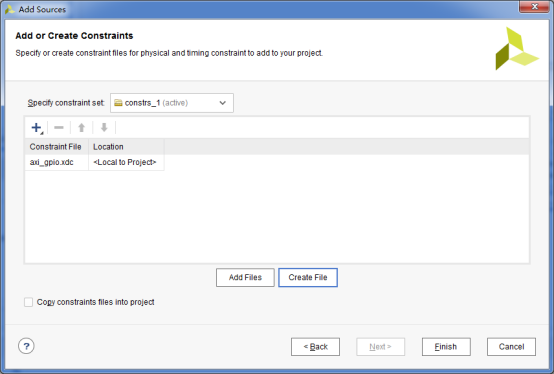

添加xdc文件

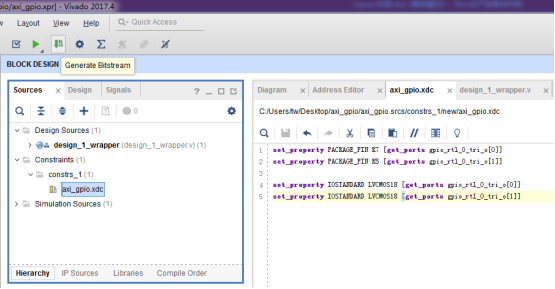

Step7 生成bit文件

Step8导出硬件配置文件

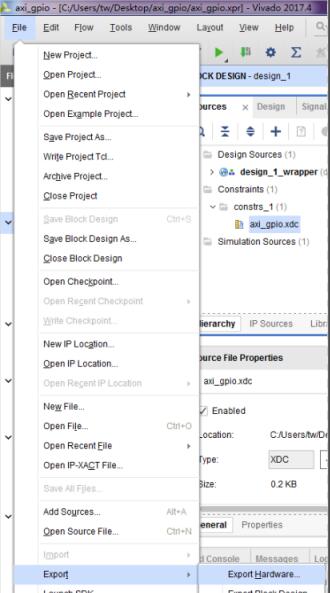

点击菜单栏上的 File->Export->Export Hardware->OK 导出硬件配置文件

Step9 启动SDK,新建fsbl

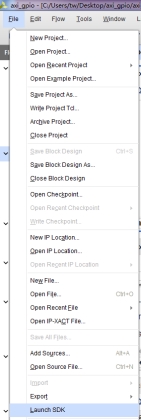

点击菜单栏上的 File->Launch SDK->OK 启动 SDK

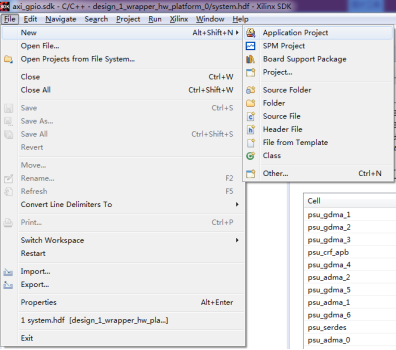

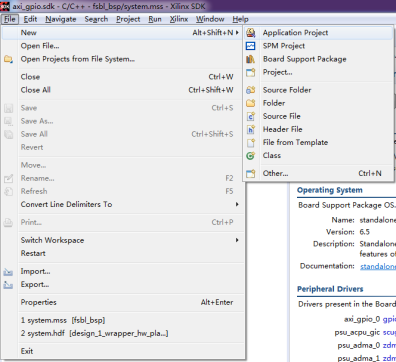

点击File-->Application Project新建工程

输入工程名为fsbl,点击Next

选择Zynq MP FSBL,点击Finish

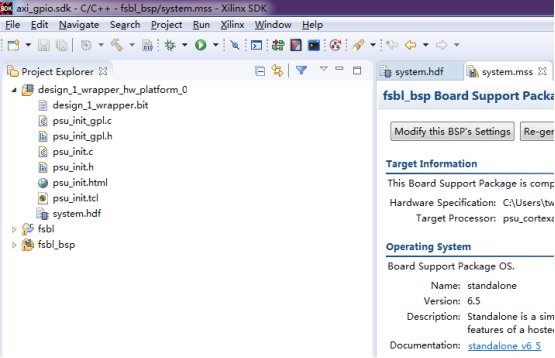

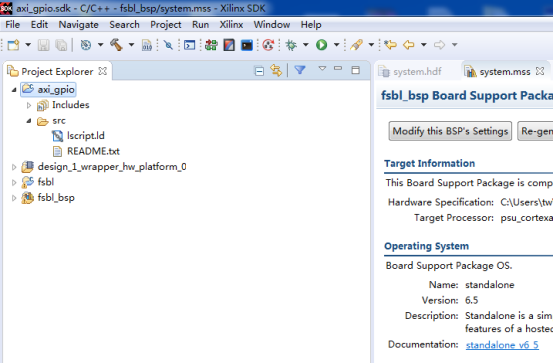

生成的fsbl如下图所示

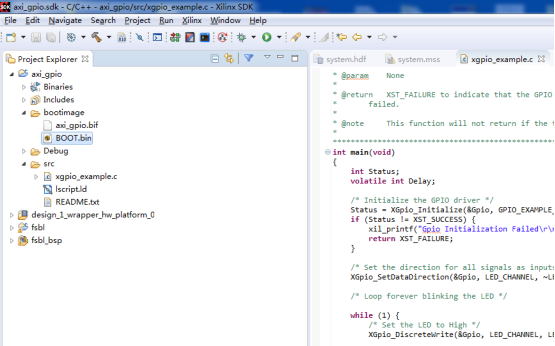

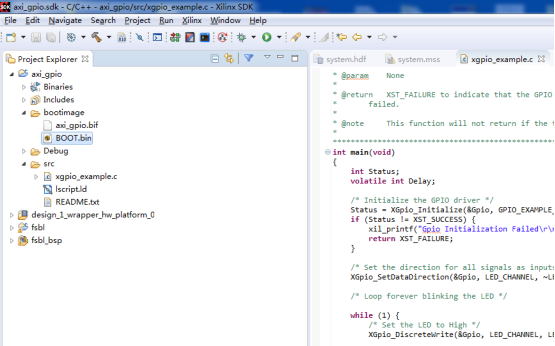

Step10 新建一个axi_gpio工程

点击File-->Application Project新建工程

输入工程名axi_gpio,点击Next

选择Empty Application模板,点击Finish

生成的axi_gpio工程,如下图所示

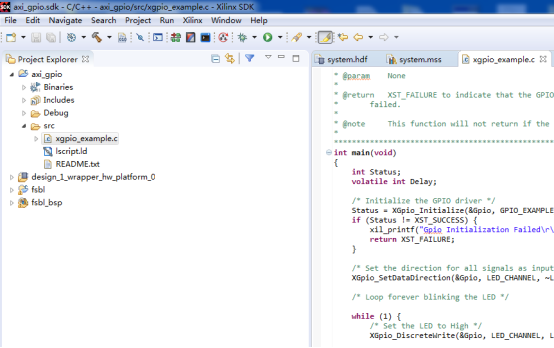

将我们提供的xgpio_example.c 文件复制到src下

Step11 生成BOOT.bin文件

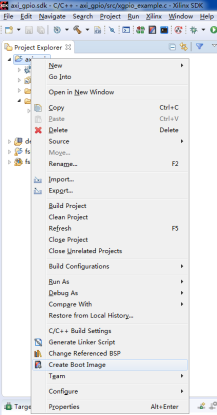

右击 axi_gpio-->Create boot Image

点击Create Image,生成BOOT.bin启动文件

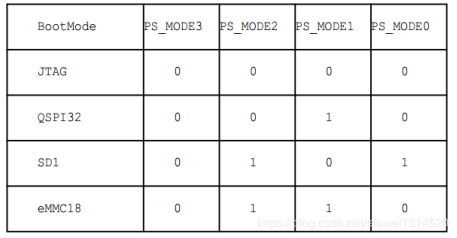

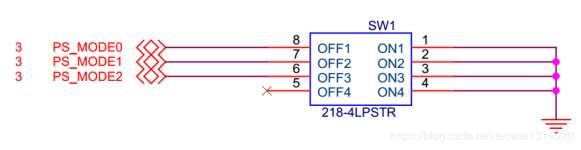

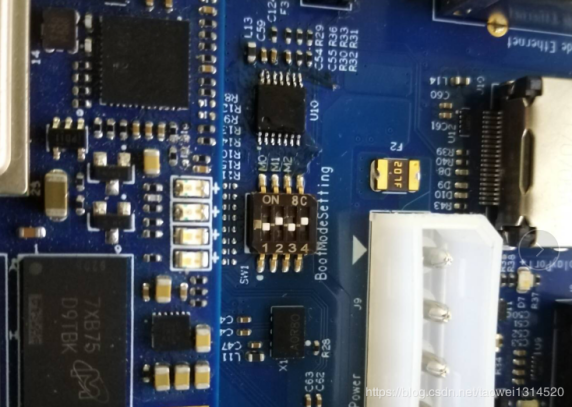

将开发板打到SD卡启动模式,然后将这个BOOT.bin文件拷贝到SD卡放到开发板上运行

开发板模式设置,这里我们设置为SD卡启动模式

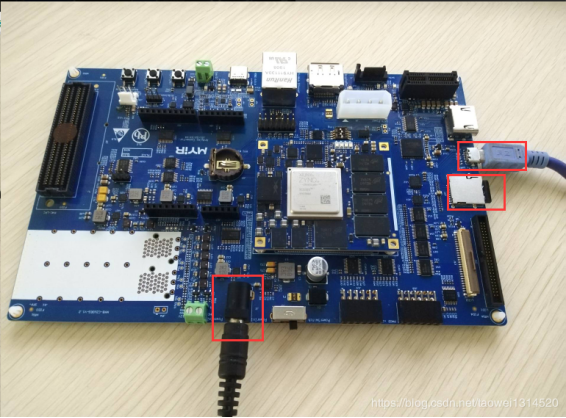

开发板连接12V电源、连接uart串口、插入SD卡

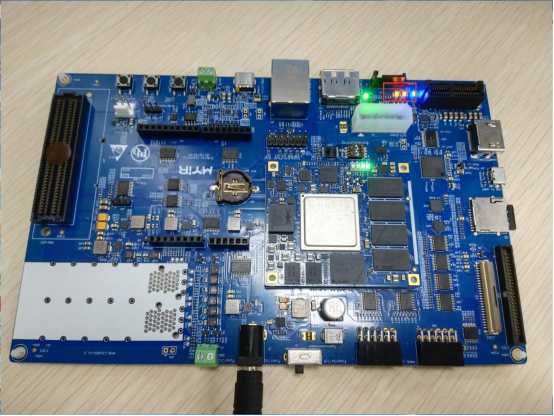

开发板上电运行,两个LED会同时闪烁

本文来自完美体育·(中国)手机网页版科技,原文地址:

/customerService/resource-list.asp?id=520,转载请注明出处。

产品中心

产品中心 服务与支持

服务与支持 关于完美体育·(中国)手机网页版

关于完美体育·(中国)手机网页版 联系我们

联系我们 关注我们

关注我们